世芯电子提高先进封装研发投资以满足高性能运算IC市场需求

导言:近年来先进封装(Advanced Package)成为了高性能运算客制化芯片(High Performance Computing ASIC)成功与否的关键。随着市场需求不断升级,世芯电子致力于投资先进封装关键技术,将其更有效率的整合到芯片设计供应链中, 以实现全客制化的合作模式。

近年来先进封装(Advanced Package)成为了高性能运算客制化芯片(High Performance Computing ASIC)成功与否的关键。随着市场需求不断升级,世芯电子致力于投资先进封装关键技术,将其更有效率的整合到芯片设计供应链中, 以实现全客制化的合作模式。

随着高阶应用市场的发展,科技系统大厂开始必须透过软硬体系统整合来实现创新,使其产品达到更强大的功能与强化的系统效能。也因为如此,现今各个系统大厂与OEM对客制化芯片(ASIC)的需求呈现高度成长。特别是在高性能运算系统芯片(SoC)领域,IC设计本身非常复杂且成本已经相当昂贵,如果再加上后端设计包含封装,测试,供应链整合等等会是更大规模的投资。在成本及效率的考虑下,各大企业选择与专业高阶ASIC设计公司合作已是必然的趋势。

高性能运算IC的成功关键取决于先进封装技术

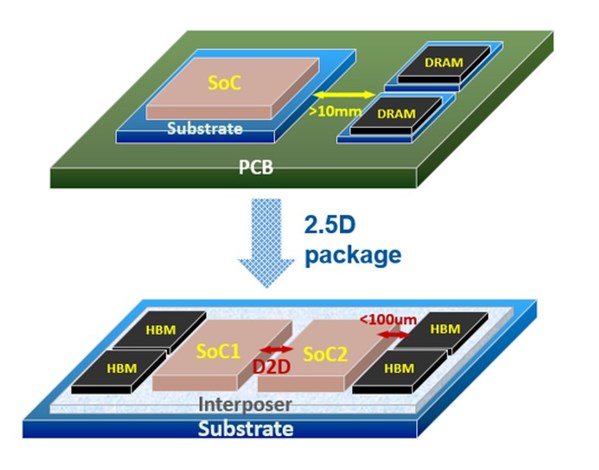

高阶应用市场的高性能运算系统芯片成长强劲,伴随的是前所未有对先进封装技术的依赖。由台积电所研发的先进封装技术CoWoS 及InFO 2.5D/3D封装对于成功部署当今的HPC SoC ASIC至关重要。CoWoS封装可以实现把数个小芯片(Chiplets)黏合在同一中介片(Interposer)同一封装基板(Substrate)上,以达到“系统级微缩”的境界,大大提升了SoC之间互连密度和性能,是科技史上的一大突破。另一先进封装技术为多芯片模组(Multi-Chip-Module,简称MCM)也是类似概念。与传统封装不同,先进封装需要与电路设计做更多的结合,加上必须整合产业的中下游,对设计整合能力是一大挑战,也是门槛相当高的投资。

先进封装CoWoS, 2.5D Package - 世芯的高性能运算设计解决方案能无缝整合系统芯片设计和先进封装技术, 进而提升互连密度和性能

世芯看到了高性能系统运算ASIC设计服务市场对先进封装需求的急速成长。“如今,各个科技大厂正大量投资于IC前端设计,以求跟自家产品完美结合以最大程度区别市场差异性及市场领先地位。他们此刻需要的是与杰出的专业ASIC设计服务公司合作,才不会让他们的大量投资及时间成本付诸流水。”世芯电子总裁兼首席执行官沈翔霖说到。

世芯是客户在高性能运算市场客制化芯片的重要伙伴

世芯电子提供的高性能运算设计方案能无缝整合高性能运算系统芯片设计和先进封装技术。世芯的MCM 于2020年量产,CoWoS 于2021 年量产。现有大尺寸系统芯片几乎是光罩的最大尺寸(Reticle Size,800mm2)。 中介片(Interposer)设计为 3~4倍于光罩最大尺寸(3~4X Reticle Size),而先进封装尺寸甚至达到 85x85mm2是现有封装技术的极限。这都是经过多项客户产品成功量产验证过的。也证明了世芯的高性能运算设计方案满足高性能运算IC市场需求,是其取得市场领先地位的重要关键。

世芯电子股份有限公司成立于2003年,总部设于台北。提供系统公司高复杂度、高产量SoC设计及量产服务。产品的应用市场包含AI人工智能、HPC高性能运算、娱乐机台、手机、通讯设备、电脑及其他消费性电子IC产品。世芯致力于为客户提供最高效益/成本比的解决方案,确保客户一次投片成功并快速将产品导入市场。世芯成立以来,已完成众多高阶制程(16纳米以下),高性能运算HPC SoC IC及先进封装(CoWoS,2.5D)量产的成功案例,并于2014年10月28日于台湾证券交易所挂牌上市(股票代号:世芯-KY: 3661)。目前在美国(硅谷)、日本(新横滨)、中国大陆(上海、无锡、合肥、广州、济南、北京)和中国台湾(新竹)拥有分部。

免责声明:

※ 以上所展示的信息来自媒体转载或由企业自行提供,其原创性以及文中陈述文字和内容未经本网站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本网站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。如果以上内容侵犯您的版权或者非授权发布和其它问题需要同本网联系的,请在30日内进行。

※ 有关作品版权事宜请联系中国企业新闻网:020-34333079 邮箱:cenn_gd@126.com 我们将在24小时内审核并处理。

更多新闻,请关注

更多新闻,请关注标签 :

相关网文

一周新闻资讯点击排行