SK海力士成功研发全球最高层238层4D NAND闪存

导言:SK海力士(或‘公司')于8月3日宣布成功研发全球首款业界最高层数的238层NAND闪存。

SK海力士(或‘公司')于8月3日宣布成功研发全球首款业界最高层数的238层NAND闪存。

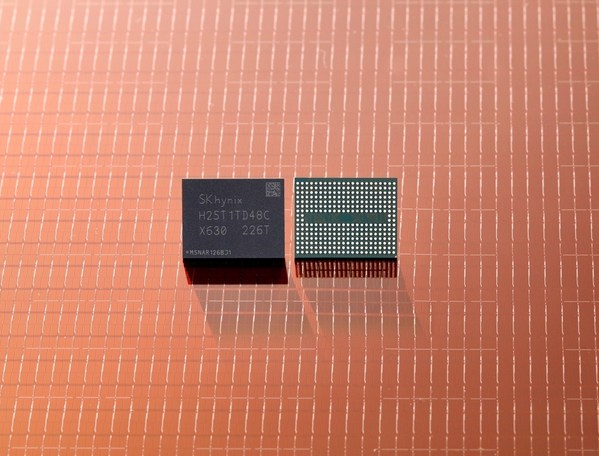

图1. SK海力士成功研发全球最高层238层4D NAND闪存

近日,SK海力士向客户发送了238层 512Gb TLC(Triple Level Cell)* 4D NAND闪存的样品,并计划在2023年上半年正式投入量产。公司表示:"自2020年12月完成176层NAND闪存研发以来,时隔仅1年7个月,SK海力士全球首次成功完成了新一代技术的研发。此次238层NAND闪存在达到业界最高堆栈层数的同时实现了全球最小的面积,其意义更加非凡 。"

* NAND闪存芯片根据每个单元(Cell)可以存储的信息量(比特,bit)可分为SLC(Single Level Cell)、MLC(Multi Level Cell)、TLC(Triple Level Cell)、QLC(Quadruple Level Cell)、PLC(Penta Level Cell)等规格。单元信息存储容量越大,意味着单位面积可以存储的数据越多。

当天,SK海力士在美国圣克拉拉举行的2022闪存峰会(Flash Memory Summit 2022)*上首次亮相了238层NAND闪存新产品。在峰会主题演讲中,崔正达SK海力士NAND闪存开发担当说道:"基于其4D NAND闪存技术,SK海力士全球首次成功研发了238层NAND闪存,进而确保了成本、性能、产品质量等层面的全球领先竞争力。公司将持续创新,并不断突破技术瓶颈。"

* 闪存峰会(FMS,Flash Memory Summit):系每年定期在美国加州圣克拉拉举办的全球闪存芯片领域的最高级别研讨会。SK海力士于本次峰会与其NAND闪存解决方案子公司Solidigm联合进行了主题演讲。

SK海力士在2018年研发的96层NAND闪存就超越了传统的3D方式,并导入了4D方式。为成功研发4D架构的芯片,公司采用了电荷捕获型技术(CTF,Charge Trap Flash)*和PUC(Peri. Under Cell)* 技术。相比3D方式,4D架构具有单元面积更小,生产效率更高的优点。

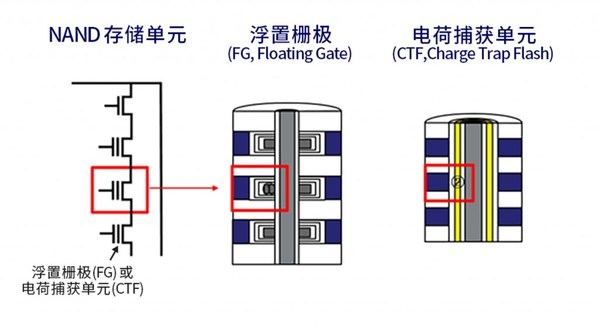

* 电荷捕获型技术 (CTF,Charge Trap Flash)

浮栅型(FG,Floating Gate)闪存技术将电荷存储在导体1)中,而CTF将电荷存储在绝缘体2)中,以解决单元间的干扰问题。因此,相比FG技术,CTF可缩小芯片的单元面积,同时提高数据的读写性能。

图2. CTF技术原理

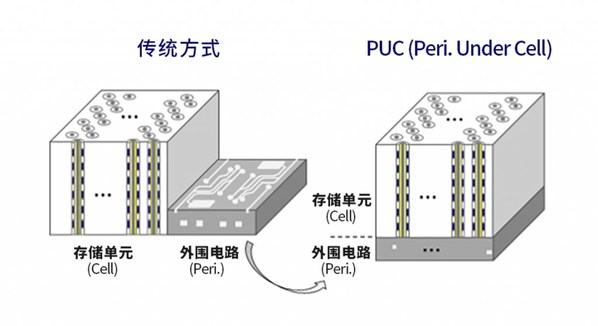

* PUC (Peri Under Cell)

将外围(Peri.)电路放置在存储单元的下方, 以最大化生产效率。

图3. PUC技术原理

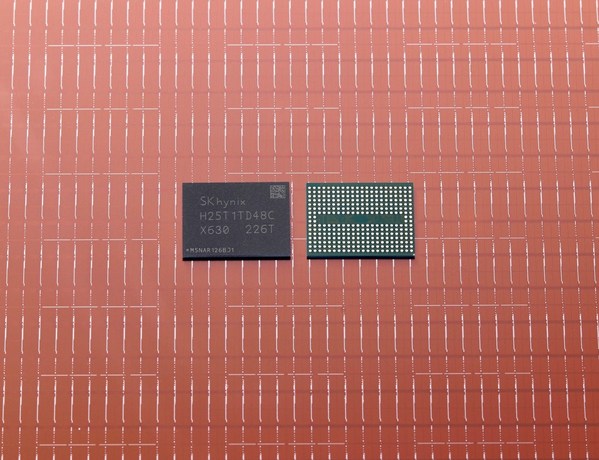

238层NAND闪存成功堆栈更高层数的同时,实现了业界最小的面积。新产品每单位面积具备更高的密度,借其更小的面积能够在相同大小的硅晶片生产出更多的芯片,因此相比176层NAND闪存其生产效率也提高了34%。

此外,238层NAND闪存的数据传输速度为2.4Gbps,相比前一代产品提高了50%,芯片读取数据时的能源消耗也减少了21%。可以说,SK海力士通过节省芯片的电力消耗,在ESG方面也取得了可圈可点的进步。

SK海力士计划先为cSSD(client SSD,主要应用范围为PC用存储设备)供应238层NAND闪存,随后将其导入范围逐渐延伸至智能手机和高容量的服务器SSD等。公司还将于明年发布1Tb 密度的全新238层NAND闪存产品,其密度是现有产品的两倍。

图4. SK海力士成功研发全球最高层238层4D NAND闪存

免责声明:

※ 以上所展示的信息来自媒体转载或由企业自行提供,其原创性以及文中陈述文字和内容未经本网站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本网站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。如果以上内容侵犯您的版权或者非授权发布和其它问题需要同本网联系的,请在30日内进行。

※ 有关作品版权事宜请联系中国企业新闻网:020-34333079 邮箱:cenn_gd@126.com 我们将在24小时内审核并处理。

更多新闻,请关注

更多新闻,请关注标签 :

相关网文

一周新闻资讯点击排行